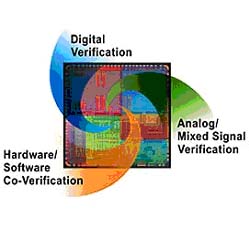

Intilop’s "design

for verification" methodology is geared to

minimize verification cycles and costly design respins.

Whether designs are targeted towards Complex FPGA

or ASIC, the methodology support either path.Their

Scalable Verification™ is the most comprehensive

Verification solution for functional verification

and merging standards. This solution provides the

industry's best language support and the most complete

path for verification, from HDL simulation to in-circuit

emulation, including support for test-benches, assertions

and functional prototypes

By enabling software and hardware engineers to work

in parallel earlier in the design process, hardware/software

co-verification significantly shortens the time-to-tape

out and enables teams to find and fix hardware bugs

before fabrication. The Seamless hardware/software

co-verification and analysis solution allows designers

to create virtual functional prototypes described

in C, RTL or mixed C/RTL early in the design process.

Using this virtual prototype, design teams can verify

that software and hardware are working together

correctly and that system performance goals are

met prior to system fabrication.

The benefits of intilop’s SoC design and verification

solutions include:

- Rapid, automated creation of SoC design descriptions and verification environments

- Verification of hardware/software interface and identification of performance bottlenecks

- Automated optimization of embedded system throughput

- Elimination of hardware prototype iterations

|

|

|