### INT-1000

## 10/100/1000 M bit MAC Engine

Product Brief, features and benefits summary

Highly customizable hardware IP block. Easily portable to Faraday-Tech's structured ASIC flow, Xilinx or Altera FPGAs

INT-1000 is highly flexible that is customizable for layer-2 through Layer-7 network security and network infrastructure applications. It is recommended for use in, among others, high performance Network security appliances and Network infrastructure appliances. It provides the key IP building block for a single high performance Giga bit Ethernet ASIC/SOC/ASSP/FPGA.

INT-1000 provides capability for enterprises to differentiate their Network security and Network infrastructure appliances from others

INT-1000 can process 1.4M packets for in-line in both directions, simultaneously, at full G-bit rate. The Direct write to Memory interface relieves the host CPU from costly DMA/buffer management execution and maintenance tasks.

- Ideal for high performance and mid performance specialized, differentiable ASICs or FPGAs for Network security or Network infrastructure applications for sustained 1G, full-duplex (2G) at 100% utilization rate processing.

- Less than 40,000 ASIC gates + on-chip memory

- $\bullet$  Fully integrated internal RAM block, synthesizable/selectable to 16KB-256KB

- 4-intelligent DMA engines.

#### G Bit High Performance MAC

- Direct Memory write and read control block, improves packet receive/transmit performance by 200-400%, by eliminating software driver to have to manage each frame and manage buffer pointers.

- Optional, On-chip DDR or SSRAM memory controller which can address 4K Bytes to 4 MB Bytes on chip or 256 MB off chip memories

- Many trade-offs for some functions performed in hardware or software

- Configurable Packet Buffer size up to 256 KB for RX and TX.

- Simple host side 32 bit/64 bit packet data transfer to/from host memory interface

- Automatic overflow into External Fast SSRAM. (optional)

- Same architecture scalable to 10Gbps.

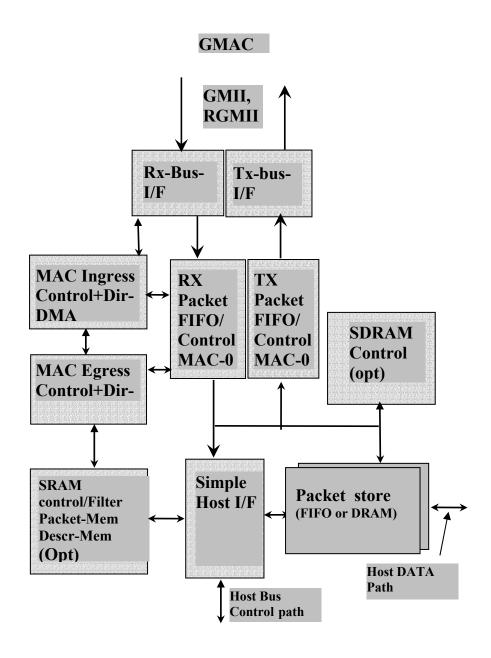

10/100/1000 M-bit, Tri-speed Ethernet MAC with generic host side interface Targeted for ASIC, SOC, Xilinx, Altera FPGAs or ASIC design flow o 802.3x compliant

- o MII or GMII interface

- o Sustained max packet transfer rate at 1G on Tx/Rx side;

- o 64 1518 Byte packets at min IFG

- Special optional features for Hardware TCP/IP acceleration:

- o TCP, UDP, and IP header checksum calculation for RX and TX

- o Hardware header parsing for Ethernet v2/802.3/IPv4/IPv6/PPPoE

- o TCP/IP header encapsulation and de-capsulation

- o Zero-copy delay from MAC- FIFO to application buffer

- o Host side bus can be 16 bit (100 MB) or 32/64 bit for 1Gbps

- o Programmable Rx FIFOs up to 256 K Bytes

- o Programmable TX FIFOs up to 256 K bytes

- o Programmable MAC address filters (optional)

- o Statistics Counters (optional)

- 10/100 M-bit MAC with generic host side interfaces Targeted for: ASIC, SOC, Xilinx, Altera FPGAs or ASIC design flow o 802.3x compliant

- o Programmable Rx FIFOs up to 64 KB

- o Programmable TX FIFOs up to 64 KB

- o Programmable MAC address filters (optional)

- o Statistics Counters (optional)

## G Bit High Performance MAC

#### Deliverables:

- Verilog source code or Netlist.

- -Verilog models for various interfaces

- Verification suite

- Test packet-traffic suite

- Detailed specs available under NDA

Intelop Corporation 4800 Great America Pkwy. Ste-201 Santa Clara, CA. 95054. www.intelop.com

Ph: 408-496-0333, Fax: 408-496-0444

# G Bit High Performance MAC

| Core Specifics                 |                                                                              |      |      |              |

|--------------------------------|------------------------------------------------------------------------------|------|------|--------------|

| Device Family                  | Virtex®-II Pro <sup>1</sup> ,<br>Virtex-4, Virtex-5                          |      |      |              |

| Speed Grades                   | • -5 for Virtex-II Pro                                                       |      |      |              |

|                                | • -10 for Virtex-4                                                           |      |      |              |

|                                | • -1 for Virtex-5                                                            |      |      |              |

| Resources Used <sup>2</sup>    | Slices                                                                       | LUTs | FFs  | Block<br>RAM |

|                                | 2267                                                                         | 3560 | 3655 | 0            |

| Provided with Core             |                                                                              |      |      |              |

| Documentation                  | Product Specification<br>User Guide<br>Getting Started Guide                 |      |      |              |

| Design File Formats            | EDIF and NGC netlist                                                         |      |      |              |

| Constraints File               | UCF                                                                          |      |      |              |

| Verification                   | VHDL test bench<br>Verilog test fixture                                      |      |      |              |

| Example Design                 | VHDL and Verilog                                                             |      |      |              |

| Design Tool Requirements       |                                                                              |      |      |              |

| Xilinx<br>Implementation Tools | ISE® v10.1                                                                   |      |      |              |

| Simulation                     | Mentor ModelSim® v6.3c<br>Cadence® IUS v6.1<br>Synopsys® vcs_mxY-2006.06-SP1 |      |      |              |

| Synthesis                      | XST 10.1                                                                     |      |      |              |

Ph: 408-496-0333, Fax: 408-496-0444