Int-1020 intelop

Silicon tested in Altera and Lattice FPGAs

## Features

- Scalable to support 2,4,8 Gigabit Ports with GMII or RGMII interface

- Integrated 1000/100/10 Mbps MAC with its own on-chip frame buffer.

- User selectable packet buffer size from 4 KB to 128 KB

- Gigabit Ports can also support 100 Mbps MII interfaces

- Host interfaces: Amba, PPC or MIPS or Generic (optional)

- Other interfaces: PCIe: x 2, 4, 8, 16. (optional)

- High Performance Layer 2 Packet Forwarding (12 M packets per second) and Filtering at Full-Wire Speed

- Less than 500 ns latency for switching/learning (64 Byte packet)

- Support for Layer-3 and Layer-4 packet classification (optional) for implementing Access control list ACLs for network security

- Maximum throughput is 8 Gbps non-blocking

- Customizable packet forwarding from any Port to any Port.

- Support for jumbo packets (opt)

- Centralized shared-memory architecture

- Integrated packet buffers

- Selectable Memory controllers per customer's performance/specifications e.g.

- Internal SRAM blocks, selectable size from 4 KB to 64 KB per port, dual port or single port SRAM blocks.

- External Fast SRAM from 256 KB to 16 M Byte Optional

- External DDR SDRAM or SSRAM Optional

- Consists of two Memory controllers at 133 MHz

- Frame Buffer Domain: one bank of ZBT-SRAM with 1 M/2 MB total(Optional)

- Switch Database Domain with 256 K/512 K SRAM

- Up to 64 K MAC addresses to provide large node aggregation in wiring closet switches

- Management interface for 'managed switching' applications

- High end Switches, Routers, security appliances

- Full 2 G bit Line rate, Packet transfer/Reception- Sustained.

- Architected for 10G MAC

- 1.6 Million, 64 Byte Packets tested through each port

- GMII or RGMII interface

- User configurable Deep FiFOs- 4K, 16k, 32k, 64k, 128k, 256k Bytes

- Direct memory storage interface

Intelop Corporation 4800 Great America Pkwy. Ste-231 Santa Clara, CA. 95054. www.intelop.com

Ph: 408-496-0333

#### Giga bit Switch

#### **Product Specifications**

Int-1020

- Statistics counters

- Configurable RAM block

- Configurable Packet Bus- 32/64/128 bits

- Configurable Int-Host bus- 32/64/128 bits

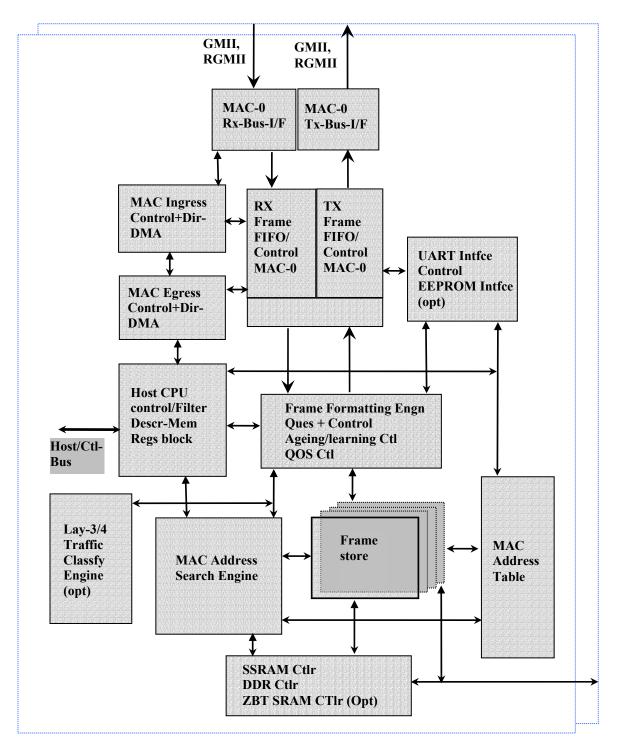

# **Giga-bit Multi-port Switch Architecture**

Intelop Corporation 4800 Great America Pkwy. Ste-231 Santa Clara, CA. 95054. www.intelop.com

Ph: 408-496-0333

### **Deliverables:**

- Verilog source code or NetList. -

- Verilog models for various components e.g. MAC, Memory, memory interface etc Verification suite -

- \_

- Test packet-traffic suite -

| Core Specifics - FPGA                 |                                                                               |       |       |              |

|---------------------------------------|-------------------------------------------------------------------------------|-------|-------|--------------|

| Device Family                         | Altera Stratix III, Virtex®-II Pro <sup>1</sup> ,<br>IV, V Virtex-4, Virtex-5 |       |       |              |

| Speed Grades                          | • Stratix - 2                                                                 |       |       |              |

|                                       | <ul> <li>-10 for Virtex-4</li> <li>-1 for Virtex-5</li> </ul>                 |       |       |              |

|                                       | • -1 for virtex-5                                                             |       |       |              |

| Resources Used <sup>2</sup>           | Slices<br>/ALMs                                                               | LUTs  | FFs   | Block<br>RAM |

|                                       | ~3100                                                                         | ~3200 | ~1500 | 16- 256      |

| Provided with Core                    |                                                                               |       |       |              |

| Documentation                         | Product Specification<br>User Guide<br>Getting Started Guide                  |       |       |              |

| Design File Formats                   | Alter-vqm, EDIF and NGC netlist                                               |       |       |              |

| Constraints File                      | UCF                                                                           |       |       |              |

| Verification                          | Verilog test bench<br>Verilog test fixture                                    |       |       |              |

| Example Design                        | Verilog                                                                       |       |       |              |

| Design Tool Requirements              |                                                                               |       |       |              |

| Xilinx/Altera<br>Implementation Tools | Quartus 8.1 ISE® v10.1                                                        |       |       |              |

| Simulation                            | Mentor ModelSim® v6.3c<br>Cadence® IUS v6.1<br>Synopsys®vcs_mxY-2006.06-SP1   |       |       |              |

| Synthesis                             | Quartus 8.1 XST 10.1                                                          |       |       |              |